報告出品方:華創證券

以下爲報告原文節選

------

一、HBM 憑高帶寬優勢成 AI 芯片主流選擇,三大存儲廠引領市場

(一)HBM 具有高帶寬優勢,AI 需求爆發驅動 HBM 快速增長

HBM(High Bandwidth Memory)即高帶寬存儲器,是一種基于 3D 堆疊工藝的 DRAM 內存芯片,具有高內存帶寬、低能耗、更多 I/O 數量、更小尺寸等優勢。隨著顯卡芯片快速發展,GDDR5 已經逐漸不能滿足對帶寬的需求,技術發展也進入瓶頸期,阻礙了顯卡芯片性能的持續提升。2009 年 AMD 開始著手 HBM 的研發,並聯合海力士在 2013 年首次實現 HBM 的制造問世。

在每個 HBM 封裝內部,多個 DRAM die 通過 TSV(硅通孔)和 Microbump(微凸塊)連接,堆疊後連接到下層 DRAM 的邏輯 die;DRAM 再通過 uBump 和 Interposer(中介層)連接 GPU 芯片。Interposer 再通過 Bump 連接到 BALL,BGA ball 再連接到封裝基板上。

HBM 技術快速叠代,向更大帶寬、更快傳輸速率演進。2014 年推出的 HBM1 帶寬爲128Gb/s,高于 DDR4 和 GDDR5,容量爲 1GB,同時較小的尺寸能夠消耗較低的功率;海力士在 2018 年推出了 HBM2,性能是 HBM1 的 2-3 倍,帶寬達到了 307GB/s,容量擴大到了 4-8 倍。2020 年海力士又推出了 HBM2 的擴展版本——HBM2E,帶寬和容量進一步擴大,到 2022 年海力士推出並量産了全球首款 HBM3,堆疊層數達到了 8/12 層,容量已提高到了 16/24GB。2024 年 2 月,美光科技表示,其 HBM3E 內存已開始量産,並將用于英偉達的 H200 計算 GPU,預計于 2024 年第二季度發貨。HBM3E 最大容量爲36GB,每引腳最大數據速率爲 9.2Gbps,最大帶寬超過每秒 1.18TB。

大模型要求算力提升速度加快,HBM 助力突破存儲瓶頸。ChatGPT 爆火 AI 大模型迎來快速發展,引爆算力需求。GPT-3 等超大語言模型對算力的提升速度要求已經突破了後摩爾時代算力提升速度的極限,“內存牆”已成爲重要的性能瓶頸。內存牆問題不僅與內存的大小有關,還與內存的傳輸帶寬有關。在過去 20 年間硬件的峰值計算能力提高了90000 倍,即使存儲器從 DDR 發展到 GDDR6x,內存/硬件互聯帶寬也只提高了 30 倍。

HBM 相比 DDR 具有更高的帶寬和更低的功耗,是高速計算平台的最優解決方案。

HBM3 成高端 AI 訓練芯片主流選擇。目前 NVIDIA 的 A100 和 H100,分別搭載了達80GB 的 HBM2E 和 HBM3,在 Grace Hopper 芯片中,單顆芯片的 HBM 搭載容量再提升20%,達到 96GB。2024 年 GTC 人工智能大會正式發布 Blackwell 芯片,單顆芯片的 GPU顯存容量高達 192GB,搭載 HBM3E,顯存帶寬有 8TB/s。此外 AMD 的 MI300 也搭載HBM3,其中 MI300X 容量達 192GB,八顆 HBM3 堆棧帶寬達 5.2TB/s。

HBM 市場規模迎來快速增長,預計 24 年全球達 169 億美元市場空間。爲應對 NVIDIA和大型 CSP 廠商對高帶寬存儲訂單的不斷增加,各大存儲供應商持續擴大 HBM 産量,TrendForce 根據供應商當前的生産計劃進行的預測表明,到 2024 年,HBM 位元供應量將增加 260%。2023 年至 2024 年將是 AI 發展的關鍵年,將引發對 AI 訓練芯片的大量需求,從而提高 HBM 配置率。2023 年起市場主要需求將從 HBM2e 轉向 HBM3,根據TrendForce 數據及預測,2022-2024 年 HBM3 需求占比分別爲 8%/39%/60%,HBM3 憑借其卓越性能加持 ASP 顯著高于前序版本,或進一步推動 HBM 市場規模在 2024 年達到169 億美元,同比增長 288 %,屆時 HBM 占 DRAM 産業産值比重或提升至 20.1%,同比提升 11.7pct。

(二)SK 海力士獨占半壁江山,三星&美光緊隨其後

SK 海力士具備先發優勢,三星奮起直追,美光專注先進世代産品。當前 HBM 的量産廠商是三大存儲廠,2012 年海力士成功研發 HBM1 後,三星奮起直追,2016 年即宣布開始量産 4GB HBM2 DRAM,並在同年開始生産 8GB HBM2。2019 年 8 月,SK 海力士宣布成功研發出新一代“HBM2e”;2020 年 2 月,三星也正式宣布推出其 16GB HBM2e 産品“Flashbolt”,于 2020 年上半年開始量産。2021 年 10 月,SK 海力士發布了全球首款HBM3,並于 2022 年 6 月正式量産,供貨英偉達,擊敗了三星再度于 HBM 上拿到了技術和市場優勢。而另一大存儲廠商美光在 2018 年放棄 HMC 後才轉向 GDDR6 和 HBM産品的研發,將更多研發投入 HBM3E 及更先進世代産品。

SK 海力士獨占 HBM 市場半壁江山,三星有望逐步縮小差距。根據 TrendForce 數據,2022 年三大原廠 HBM 份額分別爲 SK 海力士占比 50%,三星占比約 40%,美光(Micron)占比約 10%。SK 海力士目前在 HBM3 生産方面處于領先地位,是 NVIDIA 服務器 GPU的主要供應商。由于三星從 CSP 獲得的訂單數量不斷增加,預計 2024 年三星與 SK 海力士之間的市場份額差距將大幅縮小。主要專注于 HBM3E 開發的美光科技未來兩年的市場份額可能會略有下降。

HBM 供應依然緊俏,2024 年訂單量預計持續攀升。HBM Die Size 較 DDR5 同制程與同容量尺寸大 35~45%;良率(包含 TSV 封裝良率),則比起 DDR5 低約 20~30%;生産周期(包含 TSV)較 DDR5 多 1.5~2 個月不等。HBM 生産周期較 DDR5 更長,從投片到産出與封裝完成需要兩個季度以上。因此,急欲取得充足供貨的買家需要更早鎖定訂單量,據 TrendForce 集邦咨詢了解,大部分針對 2024 年度的訂單都已經遞交給供應商,除非有驗證無法通過的情況,否則目前來看這些訂單量均無法取消。以 HBM 産能來看,三星/SK 海力士/美光至 2024 年底的 TSV HBM 月總産能有望達到 130K/120~125K/20K。

二、HBM 技術概述:TSV、MR-MUF 與混合鍵合爲關鍵工藝

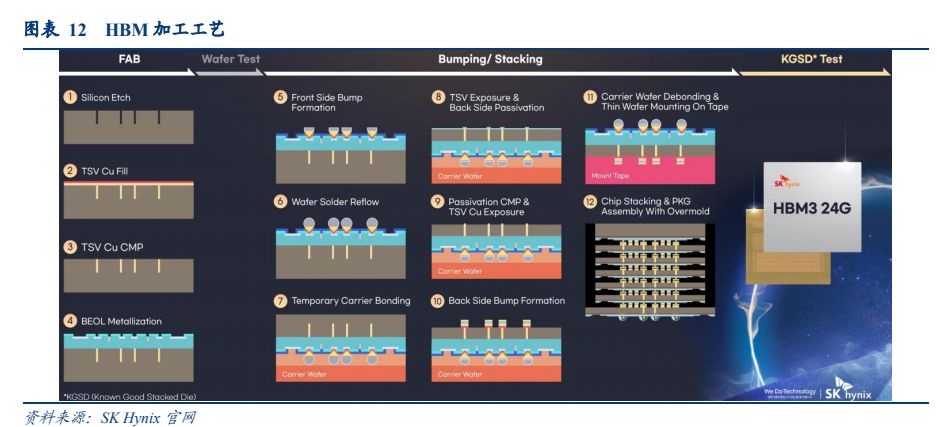

HBM 的加工流程包括前端的晶圓加工、後端的 Bumping(凸點)和 Stacking(堆疊)以及KGSD 測試。TSV 和 MR-MUF 封裝技術是 HBM 技術應用的核心工藝,混合鍵合工藝應用前景良好。

(一)TSV:HBM 制備核心工藝

TSV 封裝可以提高堆疊密度,降低互聯延遲。TSV(Through-Silicon Vias)即硅通孔技術,指在芯片上鑽孔並通過銅、鎢、多晶硅等導電物質的填充,實現芯片的垂直電氣互聯。

硅通孔封裝的優勢在于:1)可以實現較小的封裝尺寸:隨著堆疊芯片及連接引腳(Pin)的數量增加,引線複雜度提高並且需要更多空間容納引線;而硅通孔芯片堆疊不需要複雜布線,封裝尺寸更小。2)硅通孔封裝可以實現芯片直接向下方芯片發送信號,而引線鍵合封裝需先將信號傳輸至基板再傳輸至芯片,信號傳輸路徑更長,因此硅通孔封裝可以大大降低互聯延遲,提高運行速度。TSV 結合微凸點,可以在三維方向獲得最大的堆疊密度和最小的外形尺寸,同時大幅提高了芯片的速度和低功耗性能,被視爲是繼引線鍵合、載帶自動鍵合(TAB)和倒裝芯片之後的第四代封裝互聯技術。

HBM 並非一種全封裝産品,而是一種半封裝産品。當 HBM 産品被送到系統半導體制造商那裏時,系統半導體制造商會使用中介層構建一個 2.5D 封裝,將 HBM 與邏輯芯片並排排列。由于 2.5D 封裝中的基板無法提供用于支持 HBM 和邏輯芯片的所有輸入/輸出引腳的焊盤,因此需要使用中介層來形成焊盤和金屬布線,從而容納 HBM 和邏輯芯片。然後,再將這些中介層與基板連接。

TSV 工藝價值量在 HBM 封裝工藝中占比最高。根據 3DinCites 數據,配置爲 4 層 DRAM core die 和 1 層邏輯 base die 堆疊的 HBM 結構,在 99.5%和 99%的芯片鍵合良率條件下,TSV 制造和 TSV 通孔露出工藝分別占其成本的 30%和 28%。

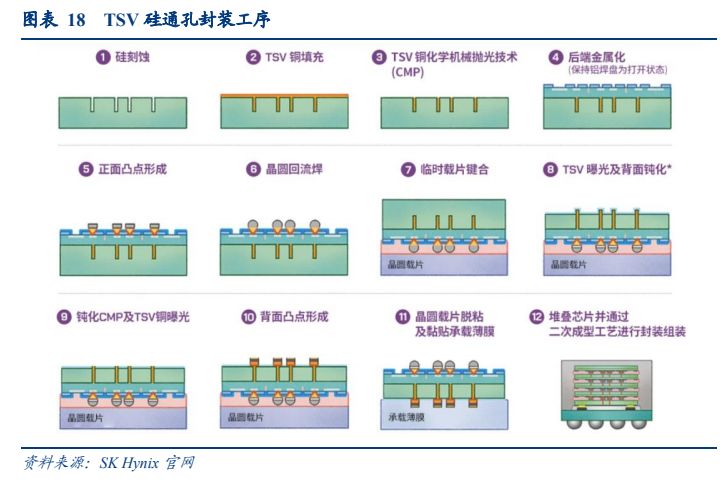

TSV 屬于前道工藝,主要由存儲原廠完成。用于生産 HBM 的 DRAM 顆粒需要在制造過程中預留 TSV 打孔的位置,屬于定制顆粒。具體封裝工藝流程:首先在晶圓制造過程中形成通孔(Via Middle)。隨後在封裝過程中,于晶圓正面形成焊接凸點。之後將晶圓貼附在晶圓載片上並進行背面研磨,在晶圓背面形成凸點後,將晶圓切割成獨立芯片單元,並進行堆疊。

中通孔(Via Middle)的制備涉及刻蝕、沉積、電鍍、抛光等工藝:首先在前道工序(Frontend of Line)中,在晶圓上制作晶體管,如互補金屬氧化物半導體等。隨後使用硬掩模(Hard Mask)在硅通孔形成區域繪制電路圖案。之後利用幹刻蝕(Dry Etching)工藝去除未覆蓋硬掩膜的區域,形成深槽。再利用化學氣相沉積工藝(Chemical Vapor Deposition)制備絕緣膜,如氧化物等。這層絕緣膜將用于隔絕填入槽中的銅等金屬物質,防止硅片被金屬物質汙染。此外絕緣層上還將制備一層金屬薄層作爲屏障。此金屬薄層將被用于電鍍銅層。電鍍完成後,采用化學機械抛光(Chemical Mechanical Polishing)技術使晶圓表面保持平滑,同時清除其表面銅基材,確保銅基材只留在溝槽中。然後通過後道工序(Back-end of Line)完成晶圓制造。

(二)MR-MUF:HBM3 領先核心技術

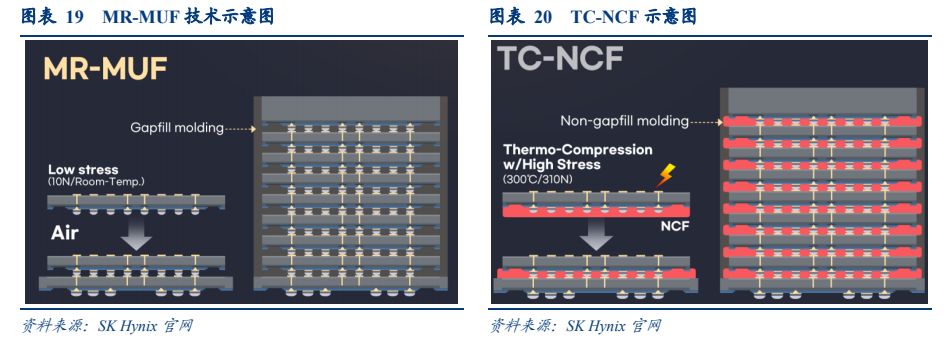

MR-MUF 相比目前主流堆疊工藝 TC-NCF 具有散熱好等優勢。MR-MUF(Mass reflow molded underfill)即批量回流模制底部填充,是將多個芯片放置在下層基板上,通過回流焊一次性粘合,然後同時用模塑料填充芯片之間或芯片與基板之間間隙的方法,該方法主要用于倒片封裝和 TSV 芯片堆疊。目前主流的堆疊工藝是用 TC-NCF 的方式,即熱壓鍵合與非導電膜(NCF,Non Conductive Film)相結合。NCF 預先貼合在晶圓表面,覆蓋凸點,在焊接過程中流動填充在芯片與芯片間,緩沖應力對芯片的影響的同時保護凸塊。

MR-MUF 避免了 TC-NCF 在穿透中所需要的高溫和壓力,使用的 EMC 塑封料具有良好的導熱性,可以將導熱率提高兩倍左右,有助于解決存儲器的散熱問題,具有顯著優勢。

MR-MUF 和 EMC 塑封料是 SK 海力士實現 HBM3 技術升級的關鍵工藝及材料。2016年,SK 海力士將批量回流焊技術應用在 8 層堆疊的 HBM2E 上,並使用具有優良導熱性的塑封料作爲間隙填充材料,改善了因存儲器帶寬增加而引起的散熱問題,同時也大幅降低了 TSV 的制造成本。對于 12 層的 HBM3 産品,堆疊的 DRAM 芯片個數從 8 個(容量 16GB)提到了 12 個(容量 24GB),容量提升了 50%,同時還要保持産品的厚度不變,需要將 DRAM 芯片打薄 40%後再進行疊加,容易導致芯片彎曲等問題,芯片間隙也縮窄13%。SK 海力士進一步改進使用的 EMC 塑封料和 MR-MUF 技術,在成功實現 12 層堆疊的同時還將散熱性提高了約 2.5 倍,重新獲得了在 HBM 市場的領先優勢。

EMC 是海力士實現 HBM3 快速叠代的關鍵材料。EMC(Epoxy Molding Compound,環氧樹脂模塑料)中文簡稱環氧塑封料,是用于半導體封裝的一種熱固性化學材料,由環氧樹脂爲基體樹脂,以高性能酚醛樹脂爲固化劑,加入硅微粉等填料,以及添加多種助劑加工而成,主要功能爲保護半導體芯片不受外界環境(水汽、溫度、汙染等)的影響,並實現導熱、絕緣、耐濕、耐壓、支撐等複合功能。根據中國科學院上海微系統與信息技術研究所數據,90%以上的集成電路均采用環氧塑封料作爲包封材料。

EMC主要構成爲硅微粉填充料。目前常見的環氧塑封料主要組成爲填充料(60%~90%)、環氧樹脂(18%以下)、固化劑(9%以下)、添加劑(3%左右)。在微電子封裝中,主要要求集成電路封裝後高耐潮、低應力、低 α 射線,耐浸焊和回流焊,塑封工藝性能好。針對這幾個要求,環氧塑封料需在樹脂基體裏摻雜無機填料,現用的無機填料基本爲二氧化硅微粉,其含量最高達 90.50%。

球形硅微粉是重要的環氧塑封料填料。填充率與硅微粉的顆粒形貌相關,硅微粉按産品顆粒形貌不同可分爲角形硅微粉和球形硅微粉。以高端芯片爲代表的大規模集成電路要求封裝材料中的填充料超細,而且要求其具有純度高、放射性元素含量低等品質,特別是對于顆粒形貌提出了球形化要求。球形硅微粉具有高耐熱、高耐濕、高填充率、低膨脹、低應力、低雜質、低摩擦系數等優越性能,成爲超大規模和特大規模集成電路封裝料中不可或缺的功能性填充材料。根據立木信息咨詢《中國電子級硅微粉市場調研與投資戰略報告(2019 版)》數據,當集成電路的集成度爲 1M-4M 時,環氧塑封料應部分使用球形硅微粉,集成度 8M-16M 時,則必須全部使用球形硅微粉。

(三)混合鍵合:未來 HBM 主流堆疊鍵合技術

互聯距離/互聯密度/導熱效率優勢加持,混合鍵合或爲未來 HBM 主流堆疊鍵合技術。目前 HBM 中所使用的 TSV 技術需要使用微凸塊垂直堆疊多個芯片(通常爲 4-12 個芯片)的方法。由于市場對高容量存儲器産品需求不斷增加,預計未來將需要 16 層甚至更高的多芯片堆疊技術。隨著層數變高,會出現翹曲和發熱等因素,同時還需滿足當下 HBM 芯片的標准厚度 720 微米。爲了實現這一目標,不僅需要減小芯片的厚度和凸塊電極的尺寸,而且在不久的將來還需要應用混合鍵合技術,去除芯片之間的填充物,使其直接連接到銅電極上。

混合鍵合(Hybrid Bonding),主要用于在芯片的垂直堆疊中實現互連,最大的特點是無凸塊,結合了金屬鍵合和非導電粘合劑(通常是氧化物或聚合物)的方法,能夠在微觀尺度上實現芯片間的直接電連接。與使用微凸塊的方法相比,混合鍵合方法可以大幅縮小電極尺寸,從而增加單位面積上的 I/O 數量,進而大幅降低功耗。與此同時,混合鍵合方法可以顯著縮小芯片之間的間隙,由此實現大容量封裝。此外,它還可以改善芯片散熱性能,有效地解決因耗電量增加而引起的散熱問題。

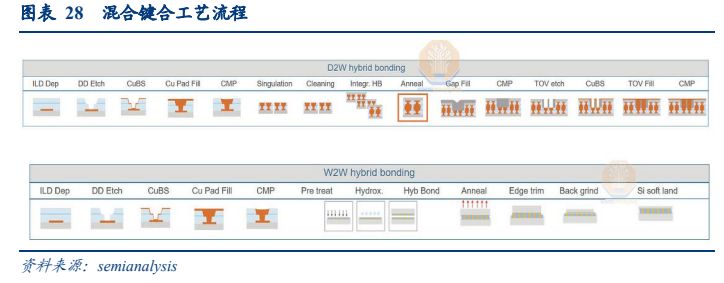

混合鍵合可以通過晶圓到晶圓 (W2W) 或芯片到晶圓 (D2W) 工藝來完成。W2W 將兩個制造好的晶圓直接鍵合在一起,此方案提供更高的對准精度、吞吐量和粘合良率,因此應用更爲廣泛。在 DRAM 領域主要使用 W2W 方案。

混合鍵合更加依賴前道制造工藝。與基于凸塊的互連相比,混合鍵合對表面光滑度、清潔度和粘合對准精度有非常嚴格的要求,因此該技術融入了十分複雜的工序,生産必須在標准接近前端晶圓廠級別的超潔淨室、自動化工廠和工藝專業知識要求的環境中進行。

混合鍵合的工藝流程還涉及許多傳統上僅由晶圓廠專用的工具,包括電鍍、CMP、等離子體激活、對准、鍵合、分割和退火,以及顆粒和缺陷的檢測工具。

混合鍵合潛在應用良多,出貨量有望快速增長。目前,混合鍵合技術已經成功應用于數據中心和高性能計算應用的高端邏輯芯片領域。AMD在其Ryzen 7 5800x的芯片設計中,采用了台積電的混合鍵合技術 SoIC,將 7nm 64MB SRAM 堆疊並鍵合到 7nm 處理器上,使內存密度增加了兩倍,成爲第一家推出采用銅混合鍵合芯片的供應商。Besi 預估,2024年邏輯芯片領域將迎來新一輪混合鍵合需求浪潮,而隨著 HBM 需求持續擡升,存儲領域將會接力邏輯芯片貢獻明顯增量,中性假設下全球 2030 年混合鍵合設備保有量有望達到 1400 台左右,混合鍵合技術爲未來芯片互聯技術的發展方向之一。混合鍵合設備的平售價將顯著高于目前最先進的 Flip chip(倒裝芯片)或 TCB 鍵合系統。據 Besi 估計,每台鍵合設備的成本在 200 萬至 250 萬歐元之間。

--- 報告摘錄結束 更多內容請閱讀報告原文 ---

報告合集專題一覽 X 由【報告派】定期整理更新

(特別說明:本文來源于公開資料,摘錄內容僅供參考,不構成任何投資建議,如需使用請參閱報告原文。)

精選報告來源:報告派科技 / 電子 / 半導體 /

人工智能 | Ai産業 | Ai芯片 | 智能家居 | 智能音箱 | 智能語音 | 智能家電 | 智能照明 | 智能馬桶 | 智能終端 | 智能門鎖 | 智能手機 | 可穿戴設備 |半導體 | 芯片産業 | 第三代半導體 | 藍牙 | 晶圓 | 功率半導體 | 5G | GA射頻 | IGBT | SIC GA | SIC GAN | 分立器件 | 化合物 | 晶圓 | 封裝封測 | 顯示器 | LED | OLED | LED封裝 | LED芯片 | LED照明 | 柔性折疊屏 | 電子元器件 | 光電子 | 消費電子 | 電子FPC | 電路板 | 集成電路 | 元宇宙 | 區塊鏈 | NFT數字藏品 | 虛擬貨幣 | 比特幣 | 數字貨幣 | 資産管理 | 保險行業 | 保險科技 | 財産保險 |